Für die kommenden Notebook-Prozessoren alias Panther Lake und die Server-Prozessoren mit Efficiency-Kernen alias Clearwater Forest bringt Intel seine aktuell laut eigener Aussage fortschrittlichste Chipfertigung zum Einsatz. Mit Intel 18A will der Chipriese wieder zur alter Stärke zurückkehren, wenn es um die Chipfertigung geht. Alle Details zu Panther Lake und Clearwater Forest präsentieren wir in den jeweiligen Artikeln. Auf das, was in Intels Fab 52 vorgehen und welche Komplexität hinter einer modernen Fertigung steckt, schauen wir uns in einem gesonderten Artikel noch an.

Neben einer grundsätzlichen Verkleinerung der Strukturen sieht Intel für Intel 18A den Einsatz einer rückseitigen Spannungsversorgung namens PowerVia und der sogenannten Gate-all-Around-Transistoren namens RibbonFET vor.

Intel 18A ist laut Intel der beste Chip-Fertigungsprozess, der sich aktuell in der Massenproduktion befindet. Mit den Vorgaben der aktuellen IDM-Strategie (Integrated Device Manufacturer) stellt die Fertigung bei Intel Foundry eine freie Entscheidung der Produktteams dar. Für Panther Lake und Clearwater Forest und deren Compute Tiles war Intel 18A offenbar die beste Wahl. Inwieweit hier auch firmenpolitische Maßgaben eine Rolle gespielt haben, lässt sich nur schwer abschätzen. Es dürfte aber klar sein, dass Intel Foundry auf die Produkte-Sparte von Intel angewiesen ist, um die eigenen Kapazitäten auslasten zu können.

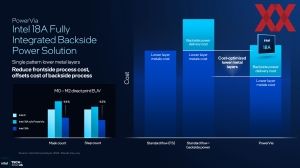

Die Umstellung auf ein BSPDN statt einer rein frontseitigen Stromversorgung verursacht zunächst Mehrkosten. Intel will diese jedoch durch einen vereinfachten Frontside-Prozess teilweise kompensieren.

PowerVia: BSPDN in Massenproduktion

Für Intel 7, Intel 4 und Intel 3 hat Intel die nötigen Frontside-Metallebenen offengelegt. Bei Intel 3 sind es bis zu 18 Lagen mit einem minimalen Pitch von 30 nm. In diesem Bereich genügt in der EUV-Lithografie eine einfache Belichtung nicht mehr, was die Herstellung der extrem dicht gepackten Ebenen spürbar verteuert.

Mit Intel 18A und PowerVia bleibt der minimale Pitch mit 32 nm zwar ähnlich klein, doch sinkt die Zahl der Prozessschritte. Diese Straffung der Frontside-Fertigung kompensiert die Mehrkosten von BSPDN weitgehend, auch wenn die Gesamtherstellung mit Rückseitenversorgung am Ende teurer bleibt.

Konkrete Zahlen lieferte Cadence zu Intel bisher grob gemachten Angaben: Für PowerVia kalkuliert man fünf Metallebenen im Backside-Prozess. Im Gegenzug lassen sich im Frontside-Prozess zwei Lagen einsparen, die zudem mit größerem Pitch ausgeführt sind. Auf den ersten Blick wirken fünf zusätzliche Backside-Lagen gegenüber zwei entfallenden Frontside-Lagen wenig vorteilhaft. Entscheidend sind jedoch die Details: Frontseitig entfallen nicht nur zwei Lagen, auch das Routing der verbleibenden Ebenen wird einfacher, was die Leitungsführung insgesamt um rund 15% reduziert. Dieser Effekt reicht bis zur Transistorebene und ermöglicht laut Cadence eine Chipflächenreduktion von etwa 10 %.

Elektrisch bringt die rückseitige Stromversorgung weitere Vorteile: Spannungseinbrüche (Vdroops) sinken um etwa 20 %. Das erhöht die Performance und verringert den Bedarf an zusätzlichen MIM-Kondensatoren.

Im Chipdesign profitieren insbesondere IP-Blöcke für I/O und PHY-Schnittstellen: Mit PowerVia ist in diesem Bereich eine, um rund 20 % geringere Leistungsaufnahme zu erwarten und die Signalqualität soll sich um etwa 15 % verbessern.

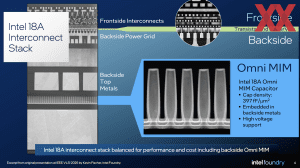

Bisher ein wenig untergegangen ist, dass Intel mit der rückseitigen Spannungsversorgung auch die Position seiner MIMs (Metal-Insulator-Metal) ändert, denn auch diese wandern auf die Rückseite. In der kommerziellen Form bezeichnet Intel diese nun als Omni MIM mit einer Kapazitätsdichte von 397 fF/µm², während aktuelle Designs je nach Multi-Plate- oder Single-Plate-Design bis zu 376 fF/µm² (auf Intel 4) erreichen können. TSMC kommt in seinen aktuellen Designs auf etwa 340 fF/µm² und liegt damit ebenfalls auf diesem Niveau.

MIMs sind für eine stabile Spannungsversorgung innerhalb des Chips eine wichtige Komponente. Gerade im HPC-Bereich helfen sie dabei den induktiven Leistungsabfall zu reduzieren und sorgen für einen stabilen Hochleistungsbetrieb der Chips.

Die rückseitige Spannungsversorgung PowerVia erlaubt eine um 10 % höhere Transistordichte und bietet einen um 30 % geringeren IR-Drop in der Versorgungsspannung.

RibbonFET: Der besser steuerbare Transistor

Wenn nicht gar schon der Fall wird der Gate-All-Around-Transistor (GAA) in den kommenden Monaten und Jahren ebenso in der Halbleitertechnik eine Revolution darstellen, wie dies mit dem FinFET ab 2012 der Fall war. Ein GAA-Transistor ist ein dreidimensionaler Feldeffekttransistor, bei dem das Gate (Steuerelektrode) den Kanal vollständig auf allen vier Seiten umschließt. Im Gegensatz zu FinFETs, wo das Gate nur drei Seiten der vertikalen Fin-Struktur kontrolliert. Die GAA-Architektur verwendet horizontal gestapelte Nanosheets oder Nanowires als Kanalstruktur, wodurch eine deutlich bessere elektrostatische Kontrolle über den Stromfluss erreicht wird.

Intels RibbonFET ist eine spezielle Implementierung der GAA-Technologie, die sich durch mehrere konfigurierbare Bandbreiten auszeichnet und ab der Fertigung in Intel 18A eingesetzt wird. Der Hauptunterschied liegt in der Flexibilität: Während Standard-GAA-Transistoren feste Nanosheet-Breiten verwenden, ermöglicht RibbonFET variable Kanalbreiten für verschiedene Anwendungen – schmalere Bänder für stromsparende Applikationen und breitere für Hochleistungsanforderungen.

Die Hauptvorteile von GAA-Transistoren umfassen eine drastische Reduzierung von Leckströmen durch die vollständige Gate-Umhüllung, bis zu 45 % geringeren Stromverbrauch bei gleicher Leistung sowie 23 % bessere Performance bei gleichem Verbrauch verglichen mit 5-nm-FinFETs. Die höhere Transistordichte ermöglicht 16 bis 35 % kleinere Chipflächen, während die verbesserte elektrostatische Kontrolle das Schalten bei niedrigeren Spannungen erlaubt.

Hartnäckig hält sich das Gerücht, auch Intel 18A könne die hochgesteckten Ziele nicht erreichen – nicht nur nicht in Form der Vorgaben für die Leistung der darin gefertigten Chips, sondern auch in der Ausbeute. Intel wiederholte aber abermals, dass Intel 18A die beste Ausbeute aller neuen Prozesse in den letzten 15 Jahren darstelle. Damit ginge man zurück bis zur Fertigung in 32 nm mit der zweiten Generation der High-k-+-Metal-Gate-Transistortechnologie aus dem Jahr 2010. Die Herausforderungen, vor denen Intel mit der Fertigung in 10 nm stand, sind für Intel 18A sicherlich keine allzu hohe Hürde.

Foveros-S und Foveros Direct 3D

Für Panther Lake und das Chiplet-Design nutzt Intel das eigenen Packaging-Technologien, genauer gesagt Foveros-S, welches schon seit sechs Jahren, also ab 2019 in Produktion ist. Die Lakefield-Prozessoren waren nicht nur die ersten hybriden Kern-Architekturen, sondern auch die ersten, die auf Foveros für das Packaging setzten.

Mit einem Bump Pitch von 36 µm oder weniger (die Varianten Fovers-R und Foveros-B sollen auf 25 µm kommen), erlaubt der Einsatz von Foveros-S einen Silizium-Interposer mit der vierfachen Größe des aktuellen Reticle-Limits und ist damit ein sogenanntes Arbeitspferd im Packaging bei Intel.

Clearwater Forest wird sowohl die Embedded Multi-Die Interconnect Bridge (kurz EMIB) als auch Foveros Direct 3D als nächsten Schritt in der vertikalen Packaging-Integration nutzen. EMIB ist ebenfalls schon seit 2019 in der Massenproduktion angekommen und damit eine bewährte Technik. Kaby Lake-G mit der Anbindung einer GPU von AMD an den Prozessor von Intel war das erste Produkte, welches EMIB verwendete.

Foveros Direct 3D stellt aber sicherlich das Highlight beim Packaging von Clearwater Forest dar. 9 µm Bump Pitch, Hybrid-Bonding mit Kupfer-zu-Kupfer-Verbindungen und vor allem die extrem effiziente Übertragung von nur 50 nJ/Bit sind sicherlich die herausstechenden Merkmale und machen einen Chip wie Clearwater Forest für Intel überhaupt erst möglich.

Bisher ist hauptsächlich Intel selbst bzw. die Produktsparte der Kunde für Intels Packaging. Seit einigen Monaten ist Intel aber verstärkt auf Kundenfang und wirbt stetig mit den eigenen Fähigkeiten. Neben dem Packaging selbst bestehen diese auch aus den Vorarbeiten wie dem Testen der Chips und Wafer.

Hardwareluxx hat die Informationen zu diesem Artikel von Intel durch Einladung des Redakteurs zur Intel Tech Tour US in Phoenix, im Bundesstaat Arizona, erhalten. Die Kosten für An- und Abreise sowie die Hotelübernachtungen wurden von Intel übernommen.