Der junge Chipauftragsfertiger Rapidus aus Japan ist nicht einmal drei Jahre alt, da beginnt die Pilotproduktion mit 2-Nanometer-Technik. Am 1. April 2025 bestätigte Rapidus den anlaufenden Betrieb in den eigenen Reinräumen. Das erste Halbleiterwerk steht in Chitose, Hokkaido. Rapidus nennt das Werk IIM-1 – IIM steht für Innovative Integration for Manufacturing.

Gegenüber IEEM Spectrum führt Rapidus aus, dass die ersten Test-Wafer schon belichtet wurden und der Hersteller bereit für die Pilotproduktion ist. Erste Prototypen will Rapidus im Juli produzieren. Rapidus-Chef Atsuyoshi Koike sagte im April, dass der Chipauftragsfertiger mit Branchenriesen wie Google, Apple, Facebook, Amazon und Microsoft über mögliche Bestellungen spricht. In einer Stellungnahme gab Rapidus später an, dass damit keine konkreten Firmen gemeint seien, sondern „die Art von Unternehmen“, mit denen Rapidus spreche.

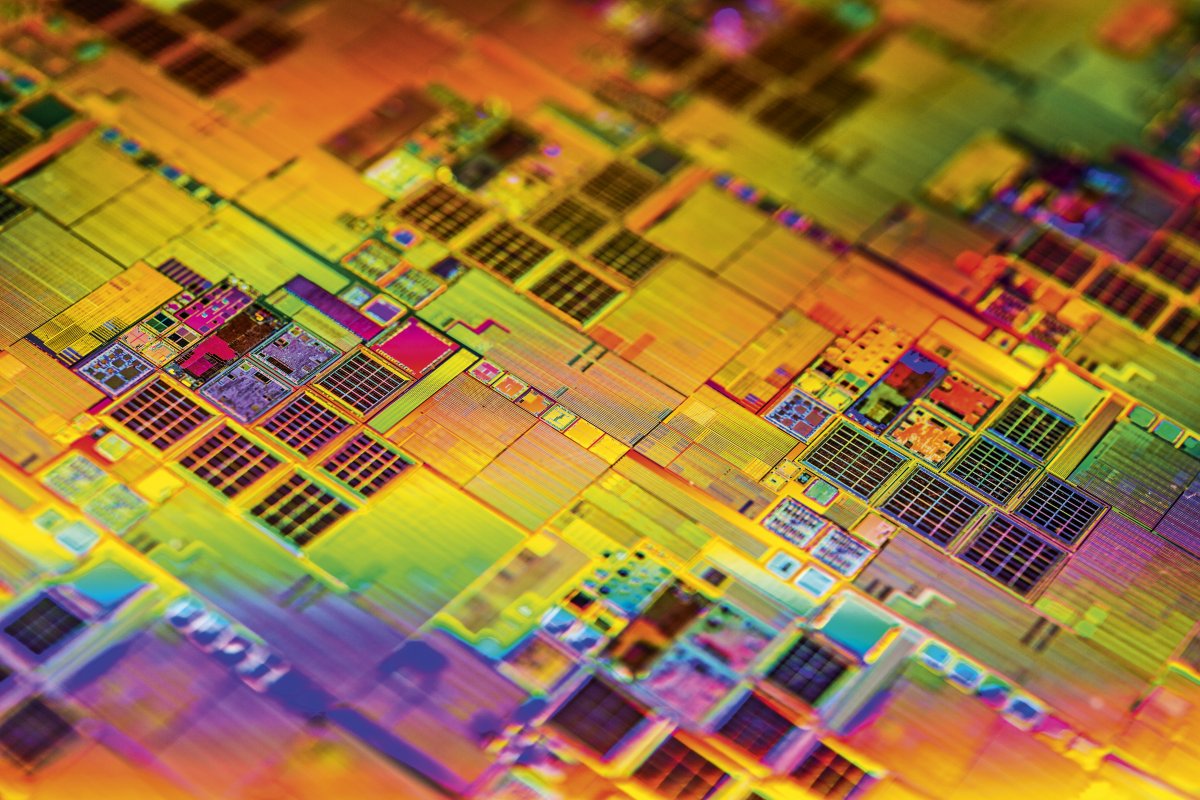

Rapidus‘ Halbleiterwerk IIM-1.

(Bild: Rapidus)

GAAFETs mit Backside Power Delivery

Die Serienproduktion mit großen Stückzahlen will Rapidus 2027 beginnen. Bis dahin wird die 2-nm-Technik nicht mehr taufrisch sein. Der Weltmarktführer TSMC etwa will schon dieses Jahr die Serienproduktion mit dem sogenannten N2-Prozess beginnen; ebenso Intel Foundry mit 18A.

Schon vor 2027 könnte Rapidus aber eine Alternative für Kleinserien darstellen. Die Japaner wollen Custom-Chips für Nischenmärkte herstellen. Sollten Apple, Google & Co. tatsächlich interessiert sein, erscheinen etwa KI-Chips für die eigenen Rechenzentren realistisch. Das wären Tausende bis Dutzende Tausend Chips, aber keine Millionen. Parallel läuft die Forschung an einem Fertigungsprozess der 1-nm-Klasse.

Zwei der drei weltweit größten Anbieter von EDA-Tools (Electronic Design Automation) für die Chipfertigung arbeiten bereits mit Rapidus zusammen: Cadence und Synopsis. Von den drei Weltmarktführer der Chip-EDA-Tools fehlt nur Siemens EDA.

Genauso wie TSMC, Samsung und Intel Foundry setzt Rapidus auf den neuen Transistortyp Gate-All-Around (GAAFETs alias Nanosheets). Auch Backside Power Delivery, also die rückseitige Stromversorgung der Transistoren, steht auf dem Plan. Für die Prozessentwicklung arbeitet Rapidus unter anderem mit IBM, Fraunhofer, der University of Tokyo, A*star IME aus Singapur und den heimischen Institutionen Leading-edge Semiconductor Technology Center (LSTC) sowie National Institute of Advanced Industrial Science and Technology (AIST) zusammen. IBM betreibt zwar keine eigenen Halbleiterwerke mehr, befindet sich bei der Transistorforschung aber weiterhin mit an der Spitze.

Die notwendigen Lithografie-Systeme stammen von ASML aus den Niederlanden. Offiziell bestätigt Rapidus den Einsatz des EUV-Systems NXE:3800E. Laut IEEE Spectrum soll aber auch ein Lithografie-System im Wert von mehr als 300 Millionen US-Dollar betriebsbereit sein. So teuer sind ausschließlich EUV-Systeme mit hoher numerischer Apertur (High-NA EUV), die die bis dato feinsten Strukturen belichten können. So ein Exemplar kostet rund 350 Millionen Euro – ein normaler EUV-Belichter 150 Millionen bis 200 Millionen.

Milliardeninvestitionen

Nominell investieren die japanischen Firmen Denso, Kioxia, MUFJ Bank, NEC, NTT, Softbank, Sony und Toyota in Rapidus. Während von ihnen umgerechnet aber nur Millionenbeträge geflossen sein sollen – in der Welt moderner Halbleiter ist das so gut wie nichts –, kommt das meiste Geld von der japanischen Regierung. Bisher hat sie Rapidus mit 1,72 Billionen Yen gefördert, was nach aktuellem Umrechnungskurs rund 10,5 Milliarden Euro entspricht. Schätzungen zufolge benötigt Rapidus bis 2027 insgesamt fünf Billionen Yen beziehungsweise gut 30 Milliarden Euro, um 2-nm-Chips in Serie zu produzieren.

Nach der Produktion will Rapidus Chips künftig auch weiterverarbeiten. Dafür baut der Hersteller ein Werk für sogenanntes Advanced Packaging auf. Es geht explizit um mehrere Chiplets auf einem gemeinsamen Träger – deswegen heißt der neue Ableger Rapidus Chiplet Solutions (RCS). Auch hier arbeiten die Japaner mit IBM, Fraunhofer, der University of Toyko und A*star IME, dem japanischen Leading-edge Semiconductor Technology Center (LSTC) und National Institute of Advanced Industrial Science and Technology (AIST) zusammen.

RCS will Chips auf fortschrittliche Redistribution Layer (RDL) setzen. RDL übertragen die Daten zwischen den Chiplets, bestehen aber nicht mehr rein aus Silizium. Stattdessen sind Siliziumbrücken und andere Komponenten integriert. TSMC etwa will Teile der Stromversorgung in den RDL integrieren.

(mma)